-

PIC프로젝트/운영체제 만들기 2023. 8. 7. 19:07

글의 참고

- https://en.wikipedia.org/wiki/Programmable_interrupt_controller

- https://en.wikipedia.org/wiki/Intel_8259

- https://en.wikipedia.org/wiki/Interrupt_request_(PC_architecture)

- https://rakmaya.tripod.com/Chip8259.htm

- https://wiki.osdev.org/8259_PIC

- https://en.wikipedia.org/wiki/End_of_interrupt

- https://www.alldatasheet.com/datasheet-pdf/pdf/66107/INTEL/8259A.html

글의 전제

- 내가 글을 쓰다가 궁금한 점은 파란색 볼드체로 표현했다.

- 밑줄로 작성된 글은 좀 더 긴 설명이 필요해서 친 것이다.

글의 내용

" 8259A 는 IBM AT 혹 IBM PC 에 존재하는 ISA 버스를 기반으로 설계된 칩이다. PIC는 하드웨어 인터럽트를 전담한다. PIC 에는 소프트웨어 인터럽트라는 개념이 존재하지 않는다. PIC는 8259A 모델이 유명하다. 이 모델은 x86 PC에서 볼 수 있는 칩이다. 현재는 사우스 브릿지 칩셋에 포함되어 여전히 출시되고 있다고 한다. 그러나 현대의 PC에서는 메인 PIC로 `APIC(Advanced Programmable Interrupt Controllers)`를 사용하고 있다. PIC는 CPU 보다 먼저 인터럽트를 받아서 우선 선위를 부여해준다. 그래서 CPU가 인터럽트 우선순위에 따라 현재 실행중인 프로세스를 선점해야 말지를 정할 수 있게 해준다.

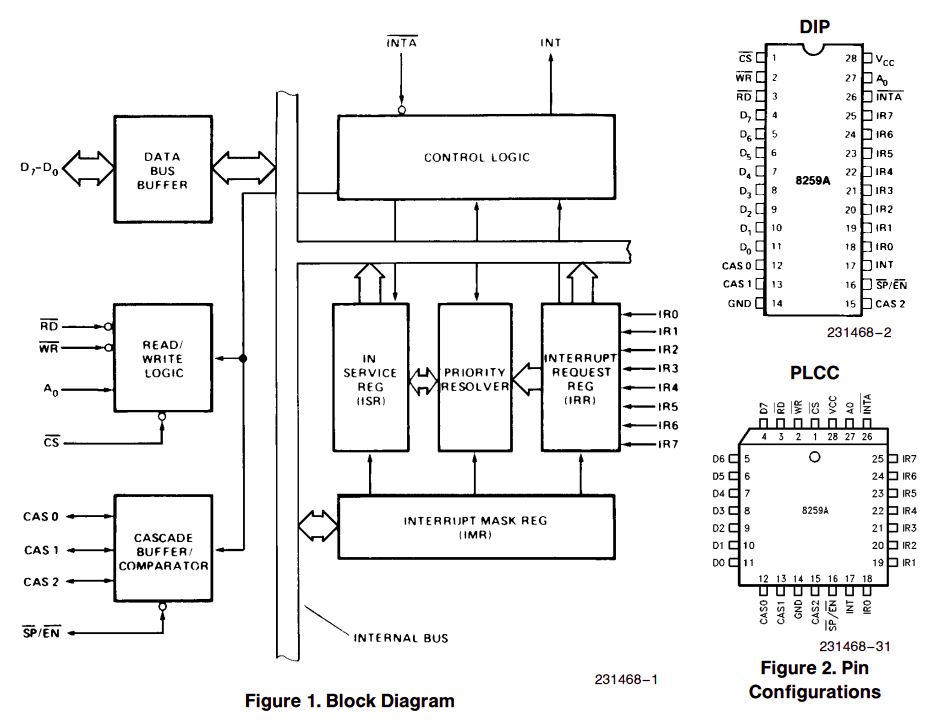

" IR0 ~ IR7 라인이 `INTERRUPT INPUT REQUEST`을 의미한다. 즉, 최대 8개의 하드웨어 직적 연결될 수 있는 것이다. 그리고 INT 핀이 HOST로 나가는 OUTPUT 핀이다. IR0 ~ IR7에 인터럽트가 들어오면 INT 라인이 트리거 되고 CPU는 PIC로 부터 인터럽트가 왔다는 것을 알게 된다.

" PIC는 `Programmable Interrupt Controller`로 약자로, x86 아키텍처에서 굉장히 중요한 칩이다. 보호 모드를 진입하고 IDT를 작성한 후, 인터럽트를 활성화하면 문제가 발생한다. 뭔가가 빠진 것이다. 아마도 예상컨대 `Double Fault`가 발생할 것이다. IDT에 8번 인터럽트이다.

" PIC의 인터럽트들은 `IRQ`로 표현을 하고 CPU의 인터럽트들은 `INT`로 표현한다. 그리고 PIC의 인터럽트를 `인터럽트 요청(INTERRUPT REQUEST)`으로 표현하고, CPU 인터럽트는 `인터럽트 벡터(INTERRUPT VECTOR)` 라고 표현한다.

" PC에서 BIOS는 옛날부터 마스터 8259의 `IRQ0 - IRQ7`을 프로세서의 `INT[08h] - INT[0Fh]`에 매핑시킨다. 그리고 슬레이브 8259의 IRQ8 - IRQ15를 `INT[70h] - INT[77h]` 에 매핑시킨다. IDT의 맨 앞에 있는 32개의 인터럽트 벡터는(`INT[00h] - INT[1Fh]`)는 프로세서가 사용하는 내부 익셉션들임에도 불구하고 BIOS는 매핑을 시켜버린다. 그래서 대 부분의 운영체제들은 마스터 8259의 인터럽트들(`INT[00h] - INT[08h]`)을 IDT의 1Fh 뒤쪽의 인터럽트들로 매핑시킨다. 즉, 마스터 8259 IRQ[7:0]를 인터럽트 테이블 0x20 - 0x27로 리매핑시키고, 슬레이브 8259 IRQ[8:15] 인터럽트 테이블 0x28 - 0x2F로 리매핑시킨다.

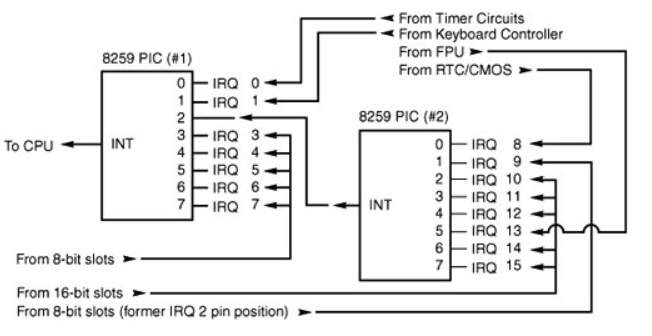

" IBM PC/AT가 등장하면서 16-bit ISA 버스가 등장했다. 그렇면서 기존에 하나만 사용하던 PIC를 2개로 늘렸다. 그래서 IBM PC/AT는 아래와 같이 2개의 PIC(마스터와 슬레이브)를 갖게 된다. 마스터 PIC의 2번째 인터럽트를 슬레이브 PIC와 연결한다. PIC에는 인터럽트의 우선 선위가 존재하는데, 번호가 작은 순으로 우선순위가 증가한다. 즉, IRQ0이 IRQ1 보다 우선 순위가 높다. 슬레이브 PIC는 마스터 IRQ2에 연결되어 있다. 즉, 슬레이브 PIC의 인터럽트는 마스터 PIC의 인터럽트 IRQ1 보다는 우선 순위가 약하고, IRQ3 보다는 우선 선위가 강하다.

출처 - https://flylib.com/books/en/4.57.1.56/1/ " 아래의 표는 마스터 8259의 인터럽트 라인을 보여준다.

- RQ 0 – system timer (cannot be changed)

- IRQ 1 – keyboard on PS/2 port (cannot be changed)

- IRQ 2 – cascaded signals from IRQs 8–15 (any devices configured to use IRQ 2 will actually be using IRQ 9)

- IRQ 3 – serial port controller for serial port 2 (shared with serial port 4, if present)

- IRQ 4 – serial port controller for serial port 1 (shared with serial port 3, if present)

- IRQ 5 – parallel port 3 or sound card

- IRQ 6 – floppy disk controller

- IRQ 7 – parallel port 1 (shared with parallel port 2, if present). It is used for printers or for any parallel port if a printer is not present. It can also be potentially be shared with a secondary sound card with careful management of the port.

" 아래의 표는 슬레이브 8259의 인터럽트 라인을 보여준다.

- IRQ 8 – real-time clock (RTC)

- IRQ 9 – Advanced Configuration and Power Interface (ACPI) system control interrupt on Intel chipsets.[3] Other chipset manufacturers might use another interrupt for this purpose, or make it available for the use of peripherals (any devices configured to use IRQ 2 will actually be using IRQ 9)

- IRQ 10 – The Interrupt is left open for the use of peripherals (open interrupt/available, SCSI or NIC)

- IRQ 11 – The Interrupt is left open for the use of peripherals (open interrupt/available, SCSI or NIC)

- IRQ 12 – mouse on PS/2 port

- IRQ 13 – CPU co-processor or integrated floating point unit or inter-processor interrupt (use depends on OS)

- IRQ 14 – primary ATA channel (ATA interface usually serves hard disk drives and CD drives)

- IRQ 15 – secondary ATA channel

- End Of Interrupt (EOI)

" `EOI`는 PIC에게 인터럽처리를 맞췄다고 CPU가 알려주는 시그널이다. 인터럽트 `EOI`가 중요한 이유는 다른 인터럽트를 막기 때문이다. 즉, EOI는 `인터럽트가 처리중이니 잠시 기다려라` 라는 의미를 가지고 있기 때문에, 처리중인 인터럽트가 끝나면 반드시 호출해줘야 한다.

An EOI is used to cause a PIC to clear the corresponding bit in the in-service register (ISR), and thus allow more

interrupt requests(IRQs) of equal or lower priority to be generated by the PIC.

...

Also, EOIs may be sent at the end of interrupt processing by an interrupt handler, or the operation of a PIC may be set to auto-EOI at the start of the interrupt handler." `EOI`는 대게 인터럽트 핸들러가 인터럽트 처리 마지막 시점에 직접 전송하거나, 혹은 PIC가 인터럽트 핸들러가 호출되는시점에 AEOI를 활성화한다. `EOI`는 슬레이브 PIC에서 인터럽트가 발생한 경우, 반드시 `EOI`는 슬레이브와 마스터 각각 전달해야 한다.

... An EOI command must be issued twice: once for the master and once for the corresponding slave.

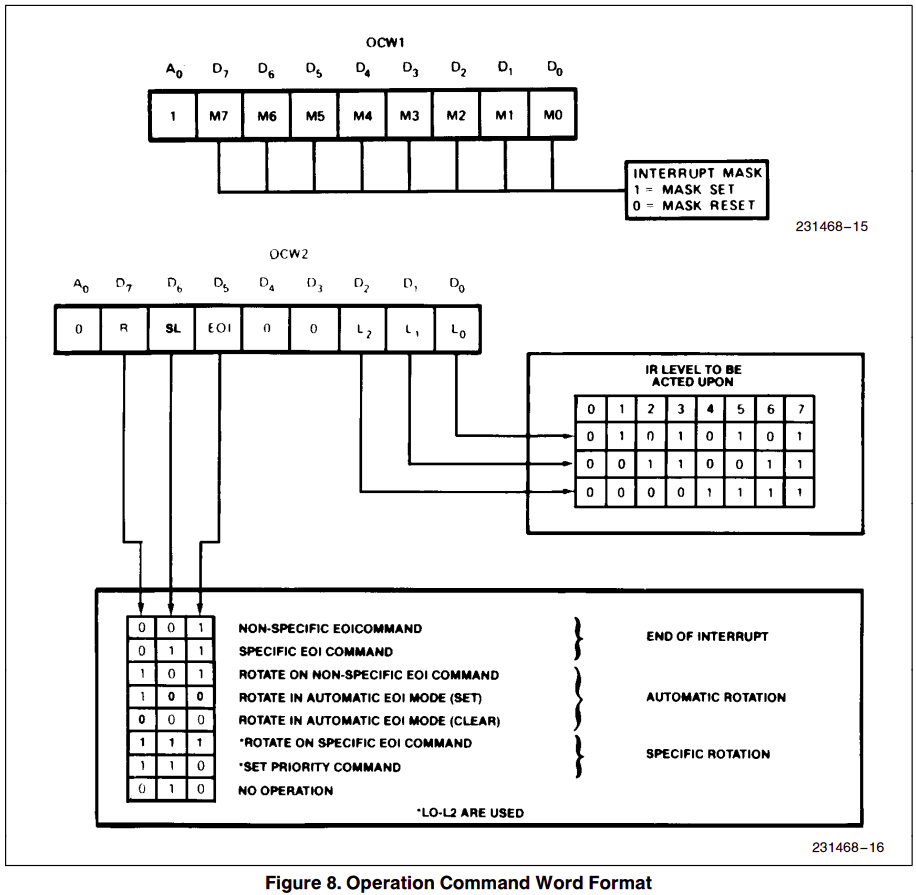

" `EOI`는 2가지 종류가 있다. 종류를 구분하는 기준은 EOI를 전송할 때, 그 다음에 실행할 인터럽트를 자동으로 선택하게 할 것이냐, 명시적 직접 지정할 것이냐다.

1" Non-specific EOI - EOI가 전송되면, 핀 번호를 우선 순위로 잡고, 자동으로 가장 높은 우선 순위의 인터럽트 IS 비트가 RESET 된다.

2" Specific EOI - `OCW2`의 SL 비트를 RESET 하고, `L0 - L2` 3비트(3비트면 8개의 인터럽트를 고를 수 있다)를 통해 어떤 인터럽트를 실행할 지 명시적으로 작성할 수 있다." 위의 2 명령어의 공통점은 OCW2를 전송한다는 것이고, 전송할 때 반드시 `EOI` 비트를 RESET 한다는 것이다.

- AEOI

" `AEOI` 는 `Automatic End Of Interrupt` 의 약자다. 말 그대로 PIC가 자동으로 `EOI`를 컨트롤 해준다는 뜻이다. ICW4에서 `AEOI`라는 비트가 SET 되면, 이 모드가 활성화된다. `AEOI` 모드는 `EOI`를 SET/CLEAR 할지를 `INTA` 핀의 상태에 따라 결정을 한다. `AEOI` 모드는 `non-specific EOI`로 동작하며, 마스터 PIC 에서만 동작한다.

- 인터럽트 우선순위

" PIC에서 인터럽트 우선순위는 번호가 작을 수록 높다. 즉, 0번인 `시스템 타이머` 인터럽트가 가장 강력하다. 여러 개의 인터럽트가 동시에 들어오게 되면, 각 IRQ들은 IRR 레지스터의 각 비트를 SET하게 된다. 그리고 가장 높은 우선순위의 인터럽트에 해당에는 벡터가 ISR 레지스터에 SET된다. 그리고 실행된다. 그리고 ISR에서 해당 비트는 `EOI`가 보내지기 전까지 `SET` 으로 남아있다. 혹은 위에서 설명한 `AEOI` 모드가 설정되어 있는 경우, `INTA` 핀 상태에 따라 `EOI`를 보낼지 말지를 정한다.

" ISR 레지스터의 특정 비트가 SET 되어 있다면, 우선 순위가 동일하거나 낮은 순위의 인터럽트는 모두 대기된다. 그러나, 현재 실행중 인 IRQ 보다 우선 순위가 높은 인터럽트가 들어오게 되면 현재 실행중인 인터럽트가 선점된다. 참고로, 우선 순위는 변경이 가능하다.

While the IS bit is set, all further interrupts of the same or lower priority are inhibited, while higher levels will generate an interrupt (which will be acknowledged only if the microprocessor internal Interupt enable flip-flop has been re-enabled through software).

- Initialization Control Word (ICWs)

: PIC에는 초기화를 위한 커맨드와 초기화 이후에 보드의 설정을 바꾸기 위한 커맨드가 존재한다. 전자를 `ICW`라고 하고, 후자를 `OCW`를 라고 한다.

- Operation Control Word (OCWs)

: 인텔 스펙에서 정의한 `OCWs`의 정의는 기본적으로 `인터럽트 동작 모드를 변경할 수 있는 커맨드`라고 정의하고 있다. 8259A 칩의 초기화가 완료된 후, 이제 인터럽트를 인식할 준비가 된다(초기화는 `ICWs`를 사용해서 완료하게 된다). 그렇면 이제 8259A가 `동작 모드` 상태가 된다. 이 때 부터는 `OCWs`를 이용해서 8259A를 컨트롤 할 수 있게 된다.

After the Initialization Command Words (ICWs) are programmed into the 8259A, the chip is ready to accept interrupt requests at its input lines. However, during the 8259A operation, a selection of algorithms can command the 8259A to operate in various modes through the Operation Command Words (OCWs).

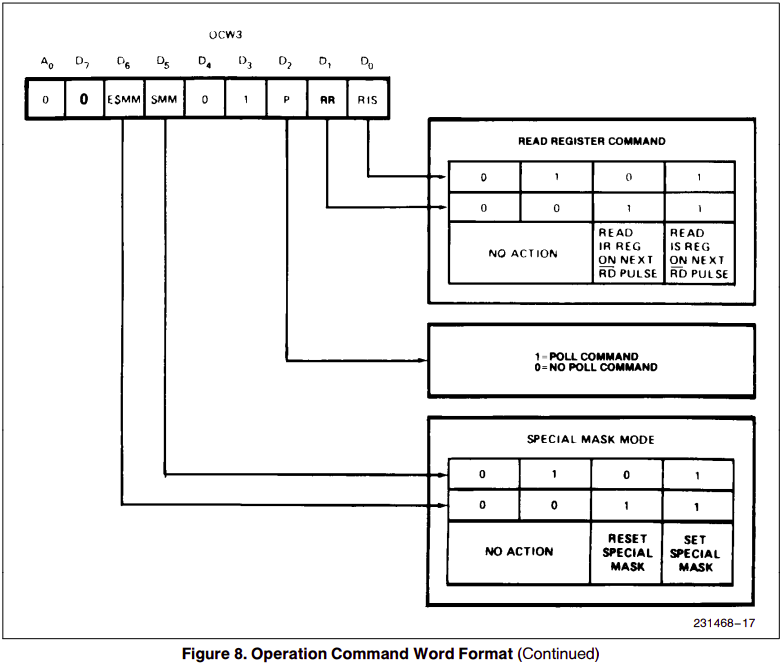

: 스펙에서 보여주는 `OCWs` 포맷은 아래와 같다. 그런데, 궁금한 점이 생긴다. `OCWs`들은 각각 별도의 주소가 있어보이지 않는 것 같다. 즉, 마스터 PIC를 통해서 OCW2, OCW3를 읽고 싶다고 할 때, 저 2개를 어떻게 구분해서 가져올까? `A0` 비트를 통해 구분한다. `A0`은 8259A에 접착되어 있는 특정 핀을 의미한다.

: 아래 포맷을 보면, `OCW2`의 5번째 비트에 `EOI`가 보인다. 나중에 `EOI`를 전송하고 싶을 때, 커맨드 명령어에 `0x20`을 보내면 된다.

: OCW3의 포맷은 아래와 같다. 주의할 점은 3번째 비트가 1이라는 점이다.

- Cascade 모드

: `Cascade 모드` 에서 인터럽트가 슬레이브 PIC가 발생했다면, 반드시 2번의 `EOI`를 전송해야 한다(마스터와 슬레이브 각각).

- 레지스터

: ISR

" ISR은 스펙에는 아래와 같이 설명되어 있다. 즉, `현재 인터럽트가 현재 인식되었다. 그래서 처리중인데, 아직 끝나지는 않았다`를 의미한다. 주의할 점은, `EOI`를 전송해야 해당 비트가 CLEAR가 된다.

In-Service Register (ISR): 8-bit register which contains the priority levels that are being serviced. The ISR is updated when an End of Interrupt Command is issued.

: IRR

" IRR은 스펙에는 아래와 같이 설명되어 있다. 쉽게, 인터럽트가 처리되기를 기다리는 레지스터라고 보면 된다. ISR 레지스터 SET 되는 인터럽트는 현재 처리 중인 인터럽트를 의미한다. IRR 레지스터에 SET 된 인터럽트들은 현재 인터럽트가 인지는 됬지만, 처리가 되지 않는 것을 의미한다. `대기 큐`에 들어있다고 보면 된다.

Interrupt Request Register (IRR): 8-bit register which contains the levels requesting an interrupt to be acknowledged. The highest request level is reset from the IRR when an interrupt is acknowledged. (Not affected by IMR.)

: IMR

" IMR 레지스터에 1로 설정된 인터럽트들은 MASK된다. 즉, 무시된다.

Interrupt Mask Register: 8-bit register which contains the interrupt request lines which are masked.

: ISR, IRR 그리고 IMR 레지스터 읽기

" IRR과 ISR을 읽기 위해서는 `OCW3`, IMR을 읽기 위해서는 `OCW1`을 사용하면 된다. 위의 `OCW3` 그림을 보면 `RR` 비트와 `RIS` 비트를 확인할 수 있다. 결국 아래 내용은 `IRR`의 내용을 알려면, OCW3의 RR = 1, RIS = 0 으로 설정해서 보내라는 뜻이다. `IRR`의 내용을 알려면, OCW3의 RR = 1, RIS = 1 으로 설정해서 보내라는 뜻이다. IMR은 커맨드가 아닌, 데이터를 읽어야 한다. 실제 환경이라면, 이 부분이 하드웨어에 상당히 의존적인 부분인 듯 한데 에뮬레이터에서는 데이터 포트를 읽음으로써 IMR 레지스터의 정보를 판단할 수 있다.

The following registers can be read via OCW3 (IRR and ISR or OCW1 [IMR]).

...

Each Interrupt Request input can bem masked individually by the Interrupt Mask Register (IMR) programmed through OCW1. Each bit in the IMR masks one interrupt channel if it is set (1). Bit 0 masks IR0, Bit 1 masks IR1 and so forth. Masking an IR channel does not affect the other channels operation.

...

The IRR can be read when, prior to the RD pulse, a Read Register Command is issued with OCW3 (RR e 1, RIS e 0.)

The ISR can be read, when, prior to the RD pulse, a Read Register Command is issued with OCW3 (RR e 1, RIS e 1).

...

For reading the IMR, no OCW3 is needed. The output data bus will contain the IMR whenever RD is active and A0 e 1 (OCW1).: ISR, IRR, IMR 을 통한 인터럽트 처리 과정

" 인터럽트가 발생하면 제일 먼저 IRR 레지스터에 대응하는 비트가 설정된다. 그리고 나면 PIC는 IMR 레지스터를 확인해서 마스크되어 있지 않으면, 해당 인터럽트를 CPU에게 던진다. 이 시점에서 ISR이 설정된다.

The PIC chip has two interrupt status registers: the In-Service Register (ISR) and the Interrupt Request Register (IRR). The ISR tells us which interrupts are being serviced, meaning IRQs sent to the CPU. The IRR tells us which interrupts have been raised. Based on the interrupt mask (IMR), the PIC will send interrupts from the IRR to the CPU, at which point they are marked in the ISR.

: 특정 인터럽트 활성화/비활성화 하기

" IMR 레지스터에 OCW1을 통해서 진행한다.

- ISA 버스

: IBM PC/AT 부터는 2개의 동일한 PIC가 존재한다. 두 모델 모두 `Intel 8259`모델이다. 각각의 PIC는 `마스터`와 `슬레이브`라고 불렸는데, IRQ0 ~ IRQ7는 마스터, IRQ8 ~ IRQ15는 슬레이브가 할당받았다. 여기서 접두사 `IRQ`는 ISA 버스 라인 핀 이름을 의미한다. 즉, PIC는 ISA 버스의 전유물로 여겨지는 모델이다.